Servicing Data

for COMPUTER BOARDS 470 (Floppy), 505 Rev. A, 510 Rev. C, 520 Rev. B, 520 Rev. C, 525, 527, 535, 550, 555, 590, 592, 594

Challenger II and III Series

Models C2-OEM C3-OEM C3-A C3-B C3-C C3-C C3-S1

## TABLE OF CONTENTS

| Block Diagrams                       | Page    |

|--------------------------------------|---------|

|                                      |         |

| 470 (Floppy) Board                   | .31,32  |

| 505 Rev. A Board                     | .41,42  |

| 510 Rev. C Board                     | 3,57,58 |

| 520 Rev. B Board                     | 81      |

| 520 Rev. C Board                     | 81      |

| 525 Board                            | 91      |

| 527 Board                            | 105     |

| 535 Board                            | 106     |

| 550 Board                            | 108     |

| 555 Board                            | 150     |

| 590 Board                            | 55,156  |

| 592 Board                            | 165     |

| 594 Board                            | 173     |

| General Servicing/Safety Precautions | 1       |

| Legends                              |         |

| 470 (Floppy) Board                   | 177     |

| 505 Rev. A Board                     | 77.178  |

| 510 Rev. C Board                     | 78.179  |

| 520 Rev. B Board                     | . 179   |

| 520 Rev. C Board                     | 179     |

| 525 Board                            | 179     |

| 527 Board                            | 79.180  |

| 535 Board                            | . 180   |

| 550 Board                            | 180     |

| 555 Board                            | 80 181  |

| 590 Board                            | 81 182  |

| 592 Board                            | Cover   |

| 594 Board                            | Cover   |

| Memory Maps                          | 28.20   |

| Model Description                    | 20,29   |

| Parts List                           | 2,0,4,0 |

| Photos                               | niu 27  |

| 470 (Floppy) Board                   | 00.04   |

| 505 Rev. A Board                     | . 33,34 |

| 510 Rev. C Board                     | ,45,46  |

| 520 Bey B Board                      | ,61,62  |

| 520 Rev. B Board                     | . /4./5 |

| 520 Rev. C Board                     | ,89,90  |

| 525 Board                            | 92      |

| 527 Board                            | . 98,99 |

| 535 Board                            | ru 112  |

| 550 Board                            | ru 122  |

| 555 Board                            | ru 138  |

| 590 Board                            | ru 154  |

| 592 Board                            | 57,168  |

| 594 Board                            | 175     |

Bunch of pages missing from here to Page 147

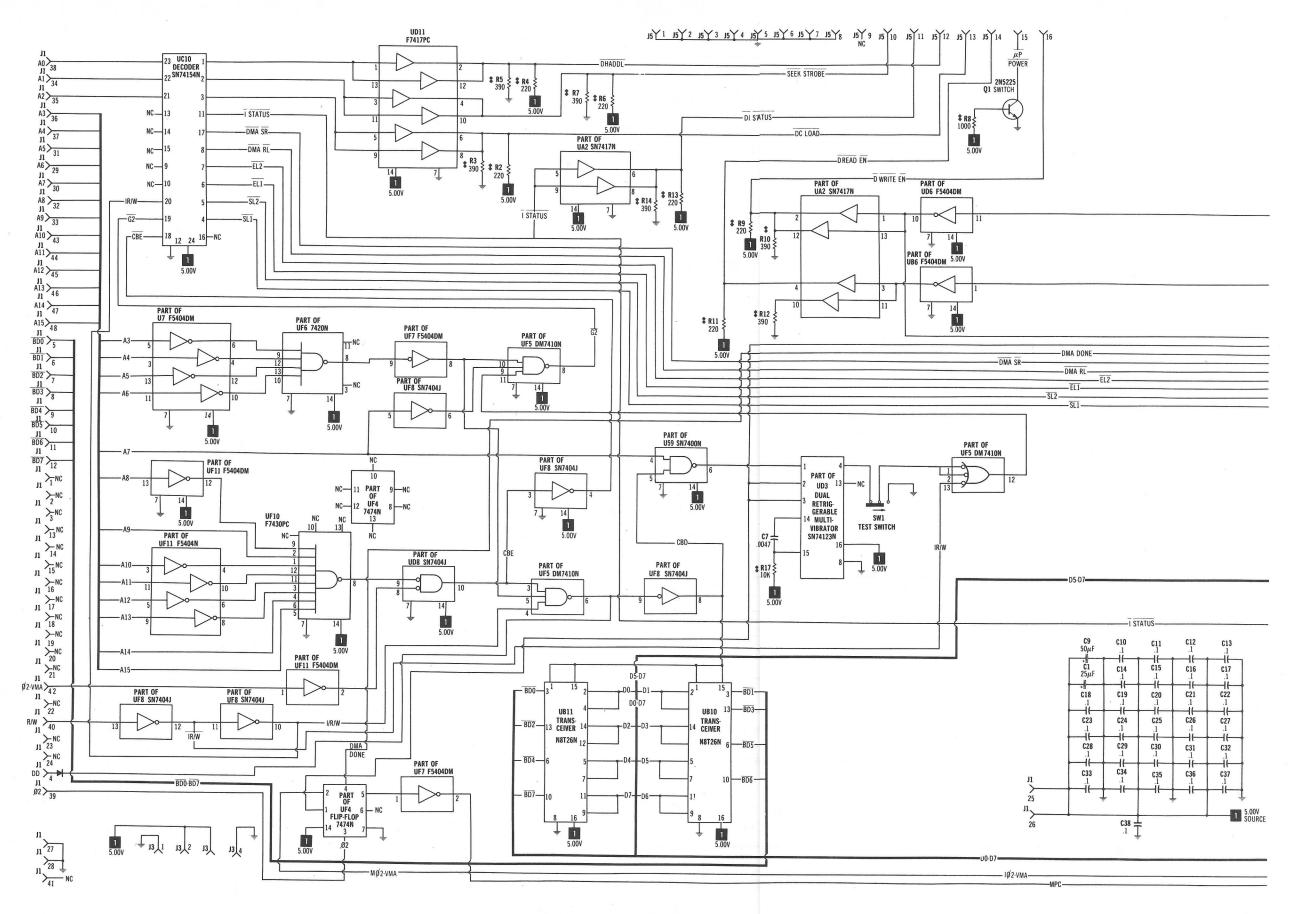

A PHOTOFACT STANDARD NOTATION SCHEMATIC WITH CIRCUITRACE<sup>®</sup> © Howard W. Sams & Co., Inc. 1980

## FOR SCHEMATIC LEGEND AND NOTES SEE PAGES 180,181 & REAR COVER.

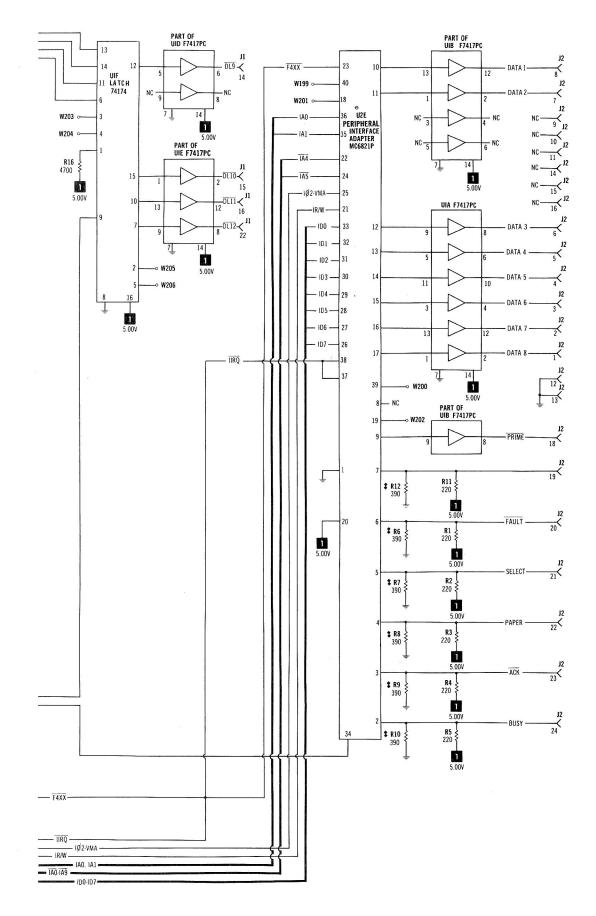

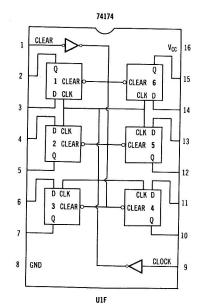

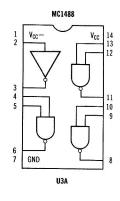

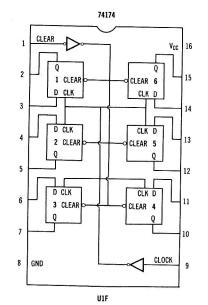

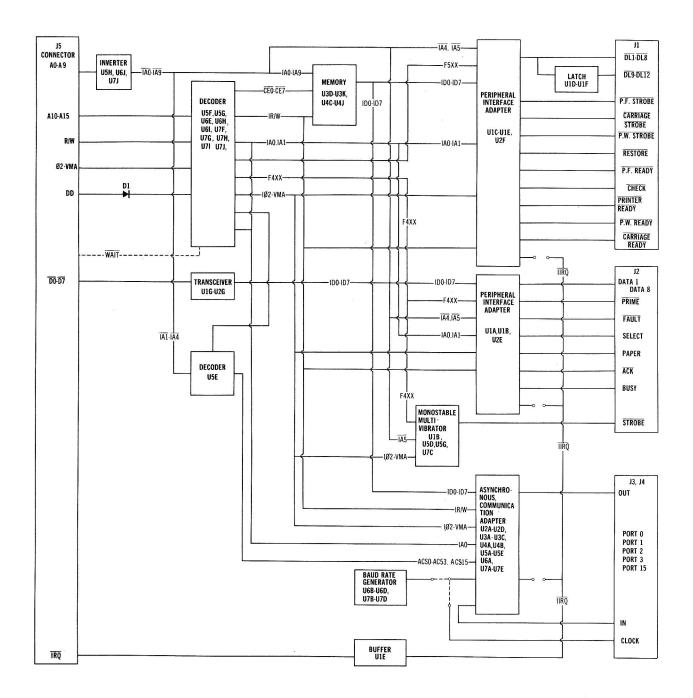

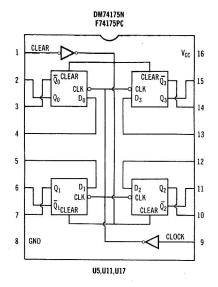

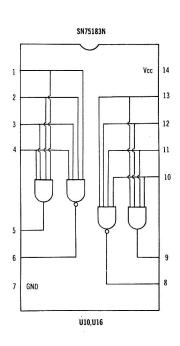

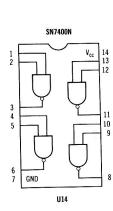

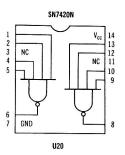

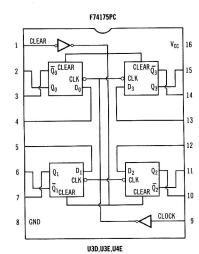

555 BOARD

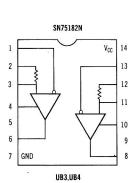

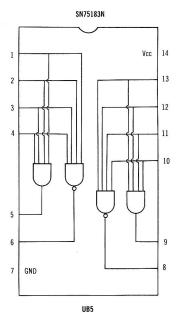

## **555 BOARD PINOUTS**

CTS GND 24 1 2 RXD DCD 23 3 CRX D0 22 4 CTX D1 21 RTS 5 D2 20 6 TXD D3 19 7 ĪRQ 18 D4 8 CS0 D5 17 CS2 9 D6 16 10 CS1 D7 15 11 RS Ε 14 12 R/W 13 V<sub>cc</sub>

6850P

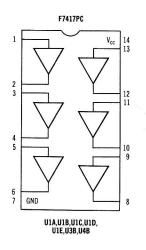

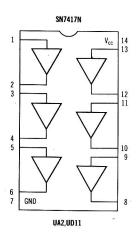

U2A,U2B,U2C,U2D,U3C

74LS14N

₫

П

π

U5B,U7A

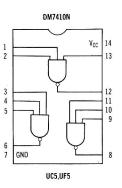

$V_{cc}$ 14 13

12

11

10

9

8

Π

₫

Π

1

23

45

6 7

GND

SN75189N 1 V<sub>CC</sub> 14 П 2 13 Д 12 11 ם 10 Π 9 7 GND 8 U4A

3

4

5

6

Г

| 1  | GND             | $\sim$ | CA1    | 40 |

|----|-----------------|--------|--------|----|

| 2  | PAO             |        | CA2    | 39 |

| 3  | PA1             |        | IRQA   | 38 |

| 4  | PA2             |        | IRQB   | 37 |

| 5  | PA3             |        | RSO    | 36 |

| 6  | PA4             |        | RS1    | 35 |

| 7  | PA5             |        | RESET  | 34 |

| 8  | PA6             |        | DO     | 33 |

| 9  | PA7             |        | D1     | 32 |

| 10 | PB0             |        | D2     | 31 |

| 11 | PB1             |        | D3     | 30 |

| 12 | PB2             |        | D4     | 29 |

| 13 | PB3             |        | D5     | 28 |

| 14 | PB4             |        | D6     | 27 |

| 15 | PB5             |        | D7     | 26 |

| 16 | PB6             | J      | ENABLE | 25 |

| 17 | PB7             |        | CS1    | 24 |

| 18 | CB1             |        | CS2    | 23 |

| 19 | CB2             |        | CS0    | 22 |

| 20 | V <sub>CC</sub> |        | R/W    | 21 |

U2E,U2F

## **555 BOARD PINOUTS**

MC6821P

CA1

CA2 39

IRQA

IRQB

RSO 36

RS1 35

RESET

DO 33

D1 32

D2 31

D3 30

D4 29

D5 28

D6 27

D7 26

ENABLE 25

> CS1 24

> CS2 23

CS0 22

R/W 21

U2E,U2F

40

38

37

34

1 GND

PA1

PA6 8

PB1

PB5 15

PB6 16

2 PA0

3

4 PA2

5 PA3

6 PA4

7 PA5

9 PA7

10 PB0

11

12 PB2

13 PB3

14 PB4

17 PB7

18 CB1

19 CB2

20 Vcc

9

8

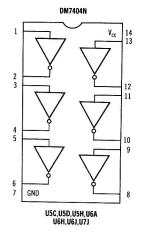

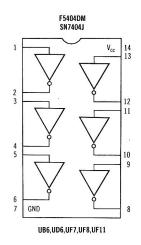

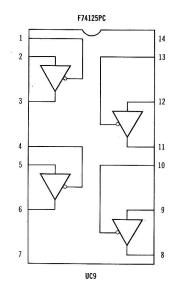

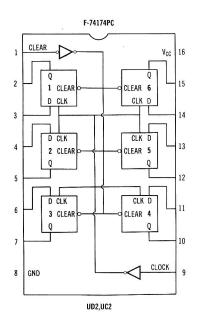

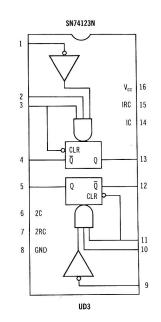

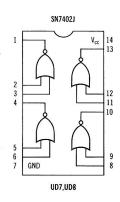

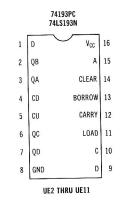

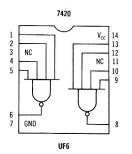

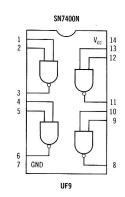

U5C,U5D,U5H,U6A U6H,U6J,U7J

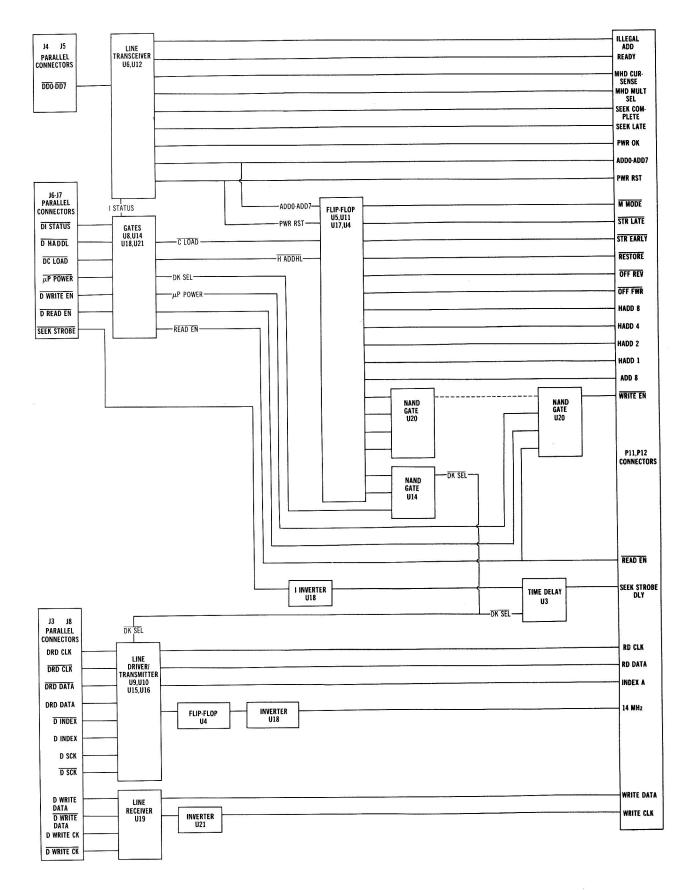

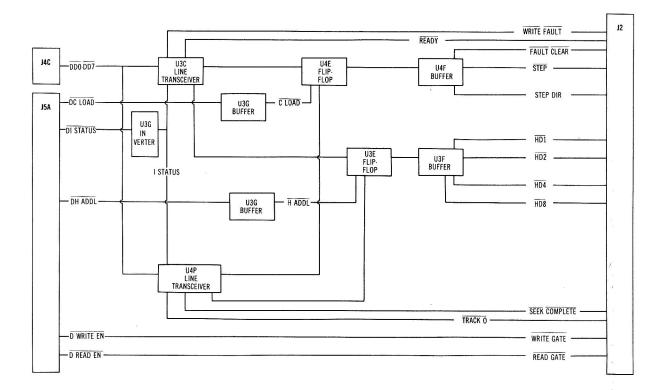

555 BOARD BLOCK

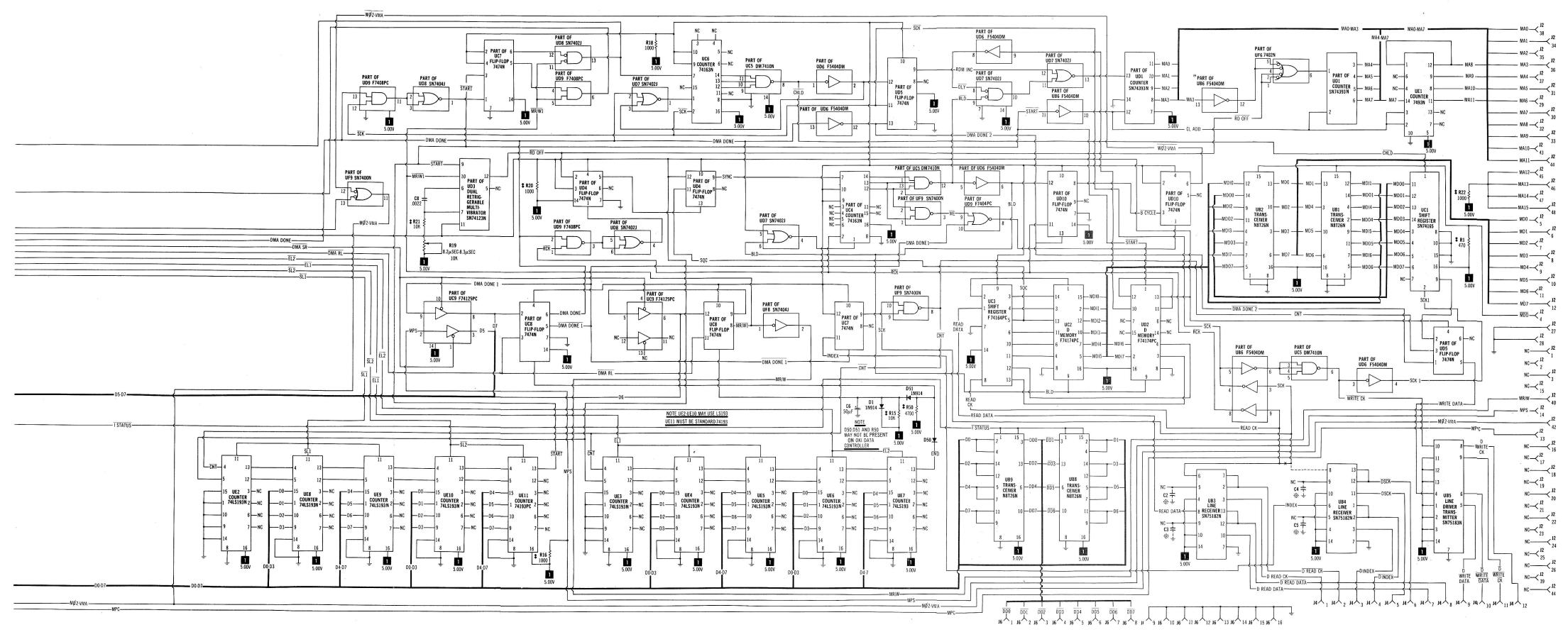

590 BOARD

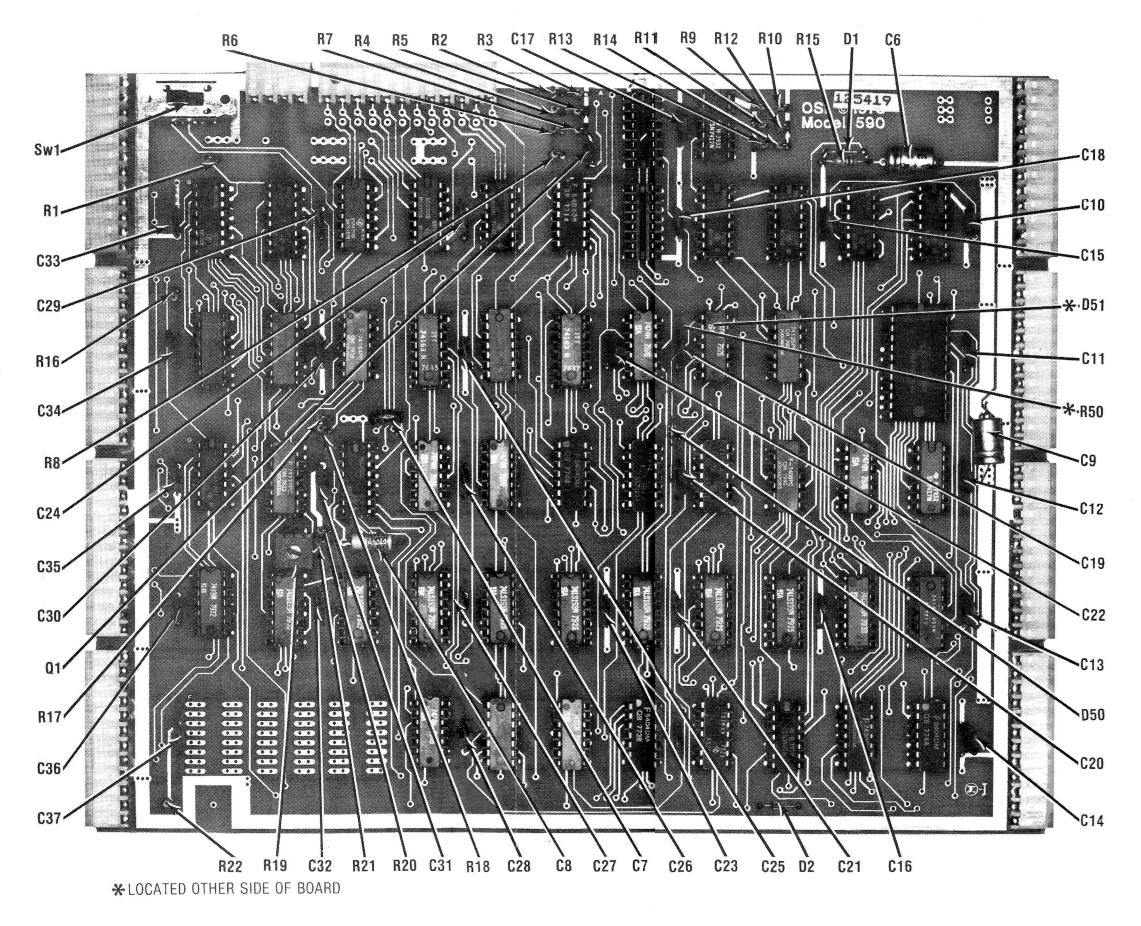

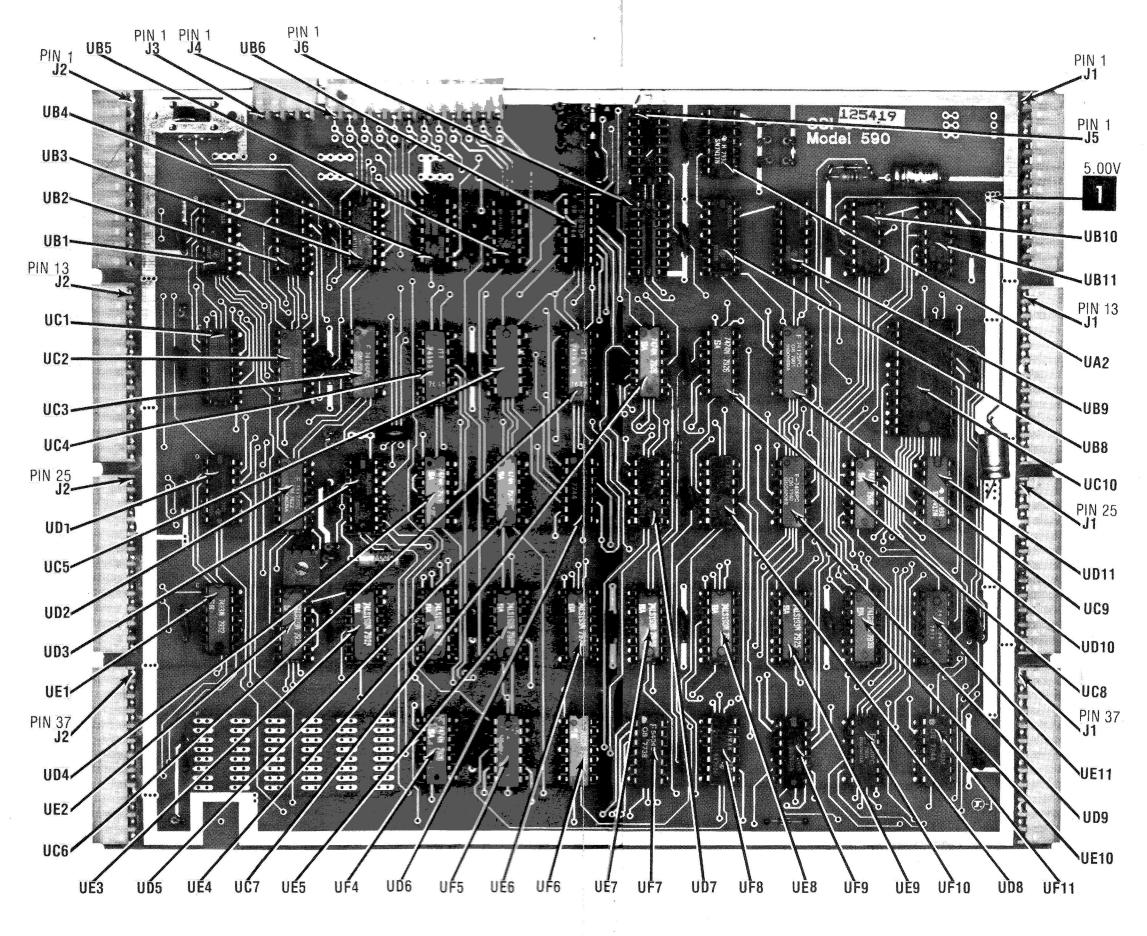

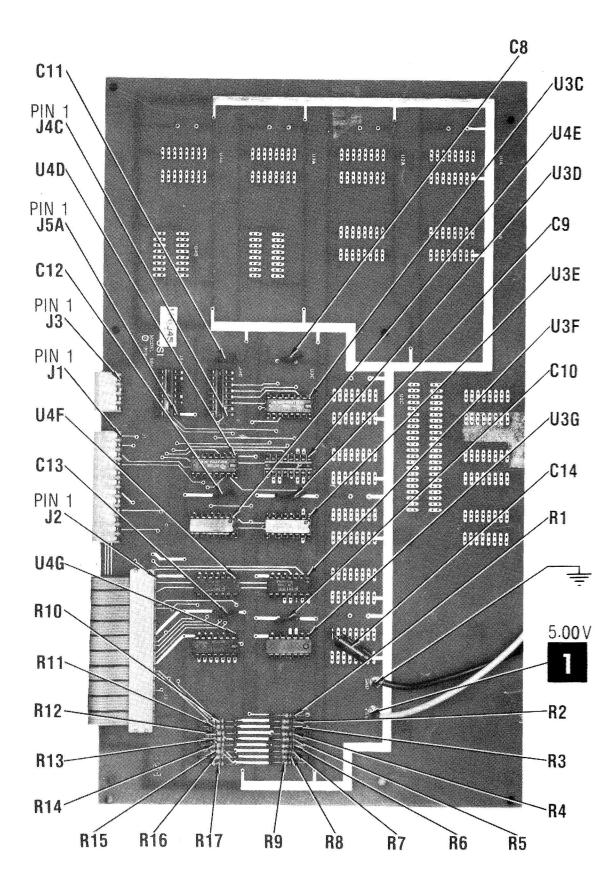

A Howard W. Sams CIRCUITRACE® Photo

590 BOARD

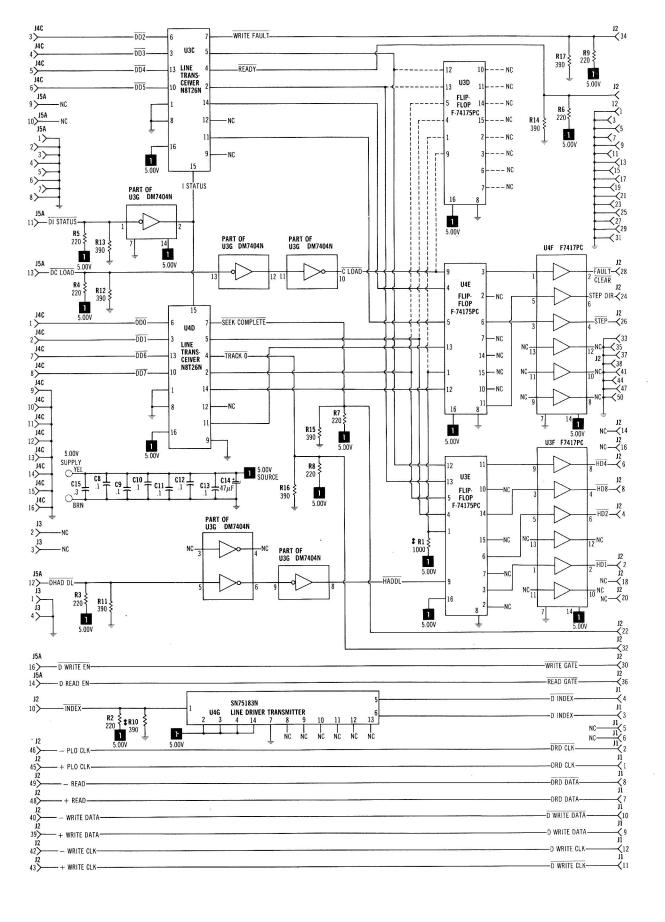

A PHOTOFACT STANDARD NOTATION SCHEMATIC

WITH CIRCUITRACE<sup>®</sup> © Howard W. Sams & Co., Inc. 1980

#### FOR SCHEMATIC LEGEND AND NOTES SEE PAGES 181, 182 & REAR COVER.

**590 BOARD**

A PHOTOFACT STANDARD NOTATION SCHEMATIC WITH CIRCUITRACE © Howard W. Sams & Co., Inc. 1980

590 BOARD

#### FOR SICHEMATIC LEGEND AND NOTES SEE PAGES 181, 182 & REAR COVER.

**590 BOARD**

160

161

162

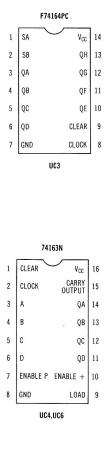

### 590 BOARD PINOUTS

590 BOARD PINOUTS (CONTINUED)

,

SN74165 SHIFT/ 1 V<sub>CC</sub> 16 LOAD CLOCK INHIBIT 15 2 CK D 14 3 E C 13 4 F B 12 5 G A 11 6 Н OH OUTPUT 7 SERIAL IN 10 8 GND OH OUTPUT 9 UC1

|    |     | SN74154N |                 |    |

|----|-----|----------|-----------------|----|

| 1  | 0   | $\sim$   | V <sub>CC</sub> | 24 |

| 2  | 1   |          | A               | 23 |

| 3  | 2   |          | В               | 22 |

| 4  | 3   |          | C               | 21 |

| 5  | 4   |          | D               | 20 |

| 6  | 5   |          | G2              | 19 |

| 7  | 6   |          | G1              | 18 |

| 8  | 7.  |          | 15              | 17 |

| 9  | 8   |          | 14              | 16 |

| 10 | 9   |          | 13              | 15 |

| 11 | 10  |          | 12              | 14 |

| 12 | GND | 2        | 11              | 13 |

|    |     | UC10     |                 |    |

|   | S     | N74393I | N               |    |

|---|-------|---------|-----------------|----|

| 1 | A     | $\sim$  | V <sub>CC</sub> | 14 |

| 2 | CLEAR |         | A               | 13 |

| 3 | QA    |         | CLEAR           | 12 |

| 4 | Q6    |         | QA              | 11 |

| 5 | QC    |         | Q6              | 10 |

| 6 | QD    |         | QC              | 9  |

| 7 | GND   |         | QD              | 8  |

|   |       | UD1     |                 |    |

# 590 BOARD PINOUTS (CONTINUED)

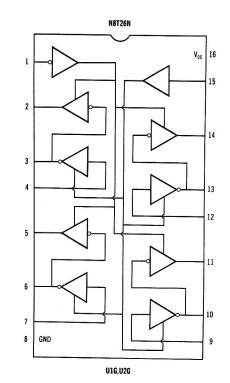

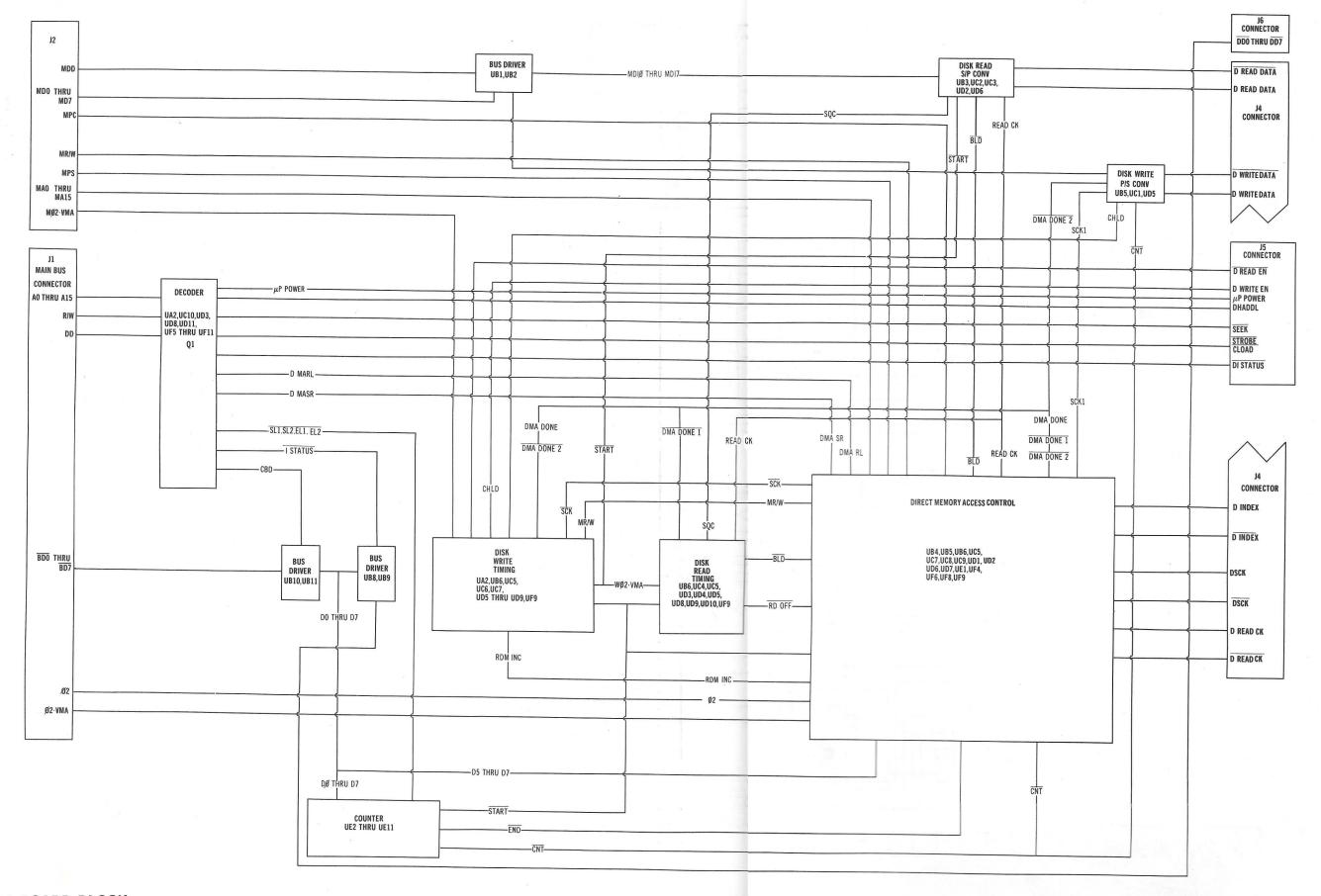

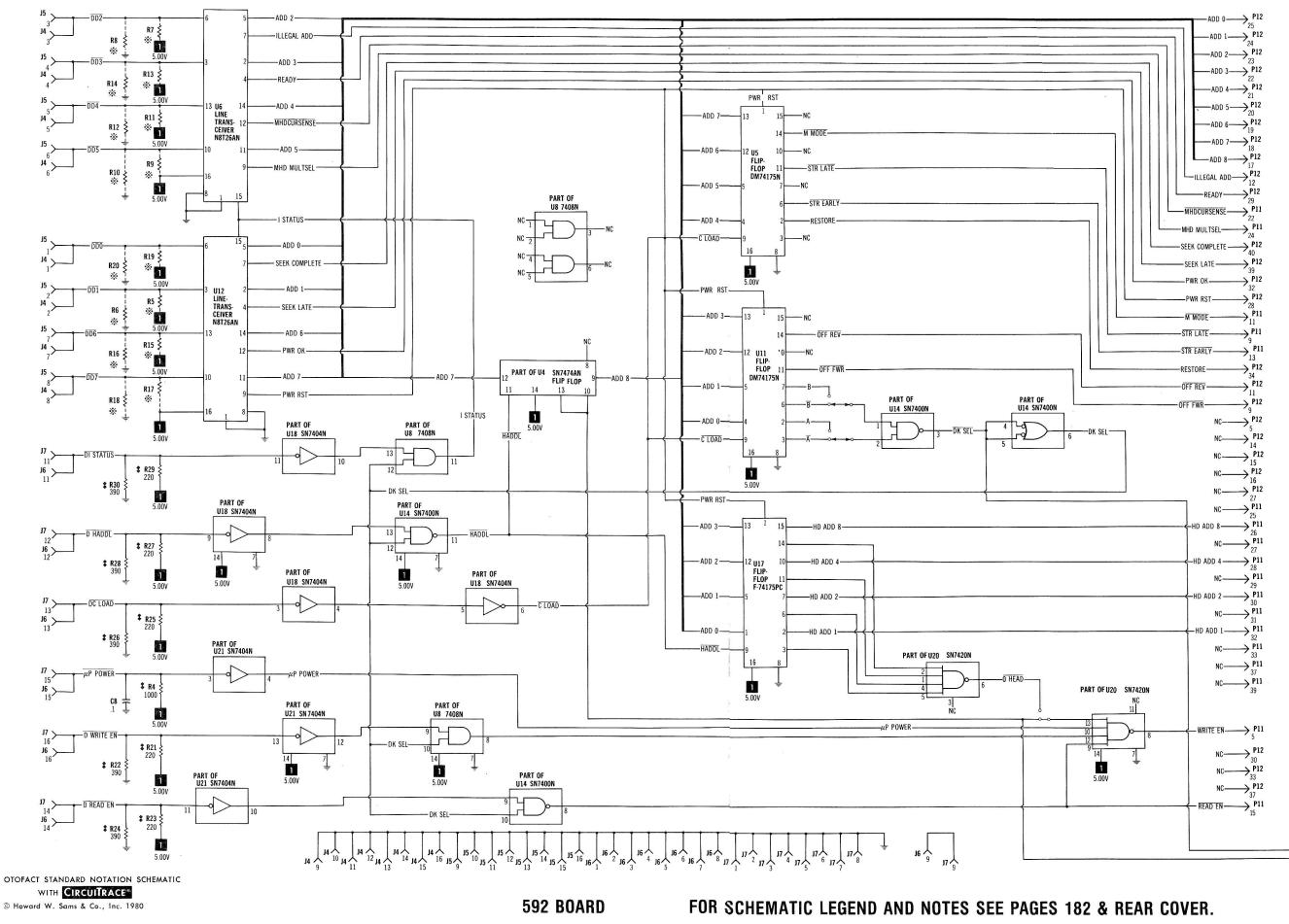

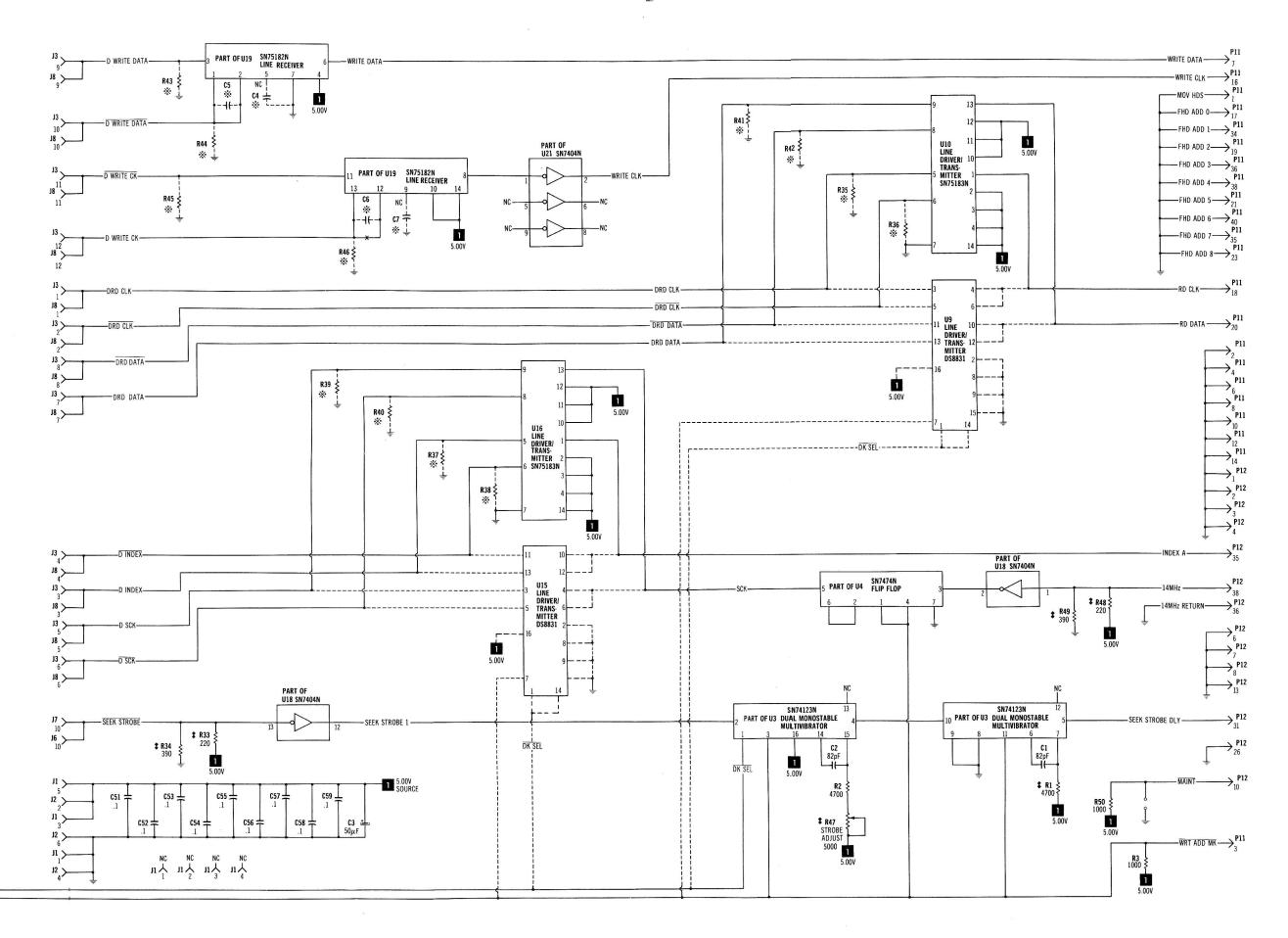

**592 BOARD BLOCK**

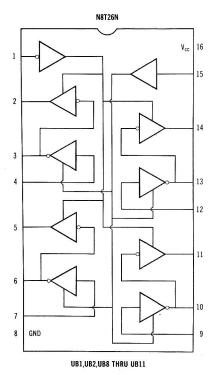

## **592 BOARD PINOUTS**

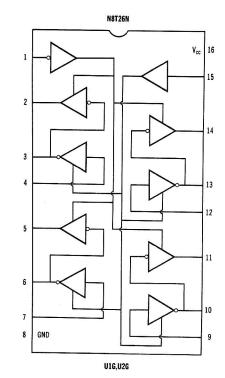

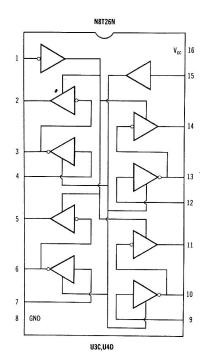

N8T26AN

8 GND

V<sub>cc</sub> 16

|   | DS8                | 831                    |    |

|---|--------------------|------------------------|----|

| 1 |                    |                        |    |

| 1 | B OUTPUT<br>ENABLE | V <sub>CC</sub>        | 16 |

| 2 | B OUTPUT<br>ENABLE | A OUTPUT<br>ENABLE     | 15 |

| 3 | OUTPUT B2          | A OUTPUT.<br>ENABLE    | 14 |

| 4 | INPUT B2           | OUTPUT A2              | 13 |

| 5 | OUTPUT B1          | INPUT A2               | 12 |

| 6 | INPUT B1           | OUTPUT <sup>®</sup> A1 | 11 |

| 7 | MODE<br>CONTROL    | INPUT A1               | 10 |

| 8 | GND                | MODE<br>CONTROL        | 9  |

|   | U9                 | ,015                   | -  |

U6,U12

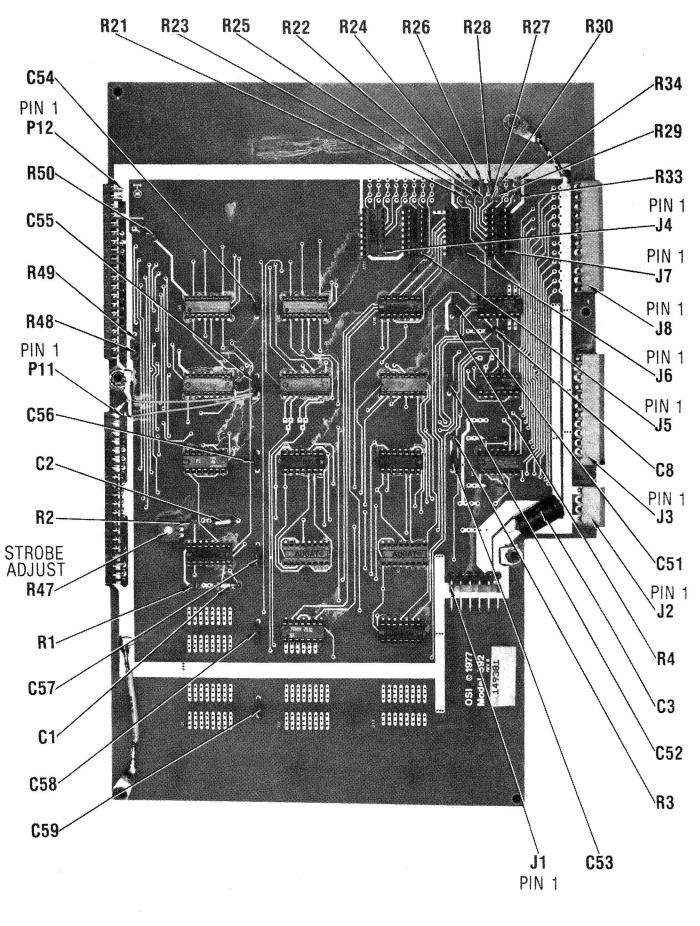

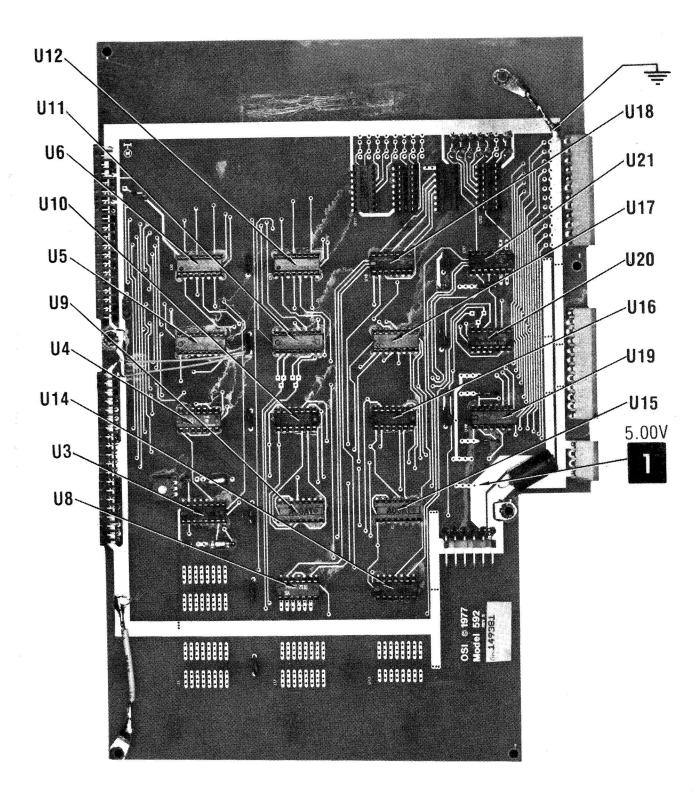

**592 BOARD**

#### 592 BOARD A Howard W. Sams CIRCUITRACE® Photo

592 BOARD

## 594 BOARD BLOCK

## **594 BOARD PINOUTS**

594 BOARD

A PHOTOFACT STANDARD NOTATION SCHEMATIC WITH CIRCUITRACE\* © Howard W. Sams & Co., Inc. 1980

594 BOARD

FOR SCHEMATIC LEGEND AND NOTES SEE REAR COVER.

| Transmit Clock       |

|----------------------|

| Valid Memory Address |

| Wait                 |

| Write Data           |

| Write Enable         |

| Write Protect        |

| Phase Two•Valid      |

| Memory Address       |

|                      |

## LEGEND FOR 505 REV. A BOARD SCHEMATIC

| AU-AIJ                                                                   | Address                                                                                                                        |

|--------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------|

| BE                                                                       | Board Enable                                                                                                                   |

| BRG                                                                      | <b>Baud Rate Generator</b>                                                                                                     |

| CA1                                                                      | Control A1                                                                                                                     |

| CA2                                                                      | Control A2                                                                                                                     |

|                                                                          | Control B1                                                                                                                     |

|                                                                          | Control B2                                                                                                                     |

|                                                                          | Clear                                                                                                                          |

|                                                                          |                                                                                                                                |

|                                                                          |                                                                                                                                |

| 0                                                                        | Chip Select D                                                                                                                  |

| E                                                                        | Chip Select E                                                                                                                  |

| CS <sub>F</sub>                                                          | Chip Select F                                                                                                                  |

| ՇՏ <sub>FL</sub>                                                         | ip Select Floppy Disk                                                                                                          |

| CS <sub>s</sub>                                                          | Chip Select Serial                                                                                                             |

| D0-D7                                                                    | Data                                                                                                                           |

| DD                                                                       | Data Direct                                                                                                                    |

|                                                                          |                                                                                                                                |

| ERASE ENABLE                                                             |                                                                                                                                |

|                                                                          | Erase Enable                                                                                                                   |

| FAULT                                                                    | Erase Enable                                                                                                                   |

| FAULT<br>FAULT RESET                                                     | Erase Enable<br>Fault<br>Fault Reset                                                                                           |

| FAULT<br>FAULT RESET<br>HEAD LOAD                                        | Erase Enable<br>Fault<br>Fault Reset<br>Head Load                                                                              |

| FAULT<br>FAULT RESET<br>HEAD LOAD<br>INDEX                               | Erase Enable<br>Fault<br>Fault Reset<br>Head Load                                                                              |

| FAULT<br>FAULT RESET<br>HEAD LOAD<br>INDEX<br>IRQ                        | Erase Enable<br>Fault<br>Fault Reset<br>Head Load<br>Index                                                                     |

| FAULT<br>FAULT RESET<br>HEAD LOAD<br>INDEX<br>IRQ<br>IR/W                | Erase Enable<br>Fault<br>Fault Reset<br>Head Load<br>Index<br>Interrupt Request                                                |

| FAULT<br>FAULT RESET<br>HEAD LOAD<br>INDEX<br>IRQ<br>IR/W                | Erase Enable<br>Fault<br>Fault Reset<br>Head Load<br>Index                                                                     |

| FAULT<br>FAULT RESET<br>HEAD LOAD<br>INDEX<br>IRQ<br>IR/W                | Erase Enable<br>Fault<br>Fault Reset<br>Head Load<br>Index<br>Interrupt Request                                                |

| FAULT<br>FAULT RESET<br>HEAD LOAD<br>INDEX<br>IRQ<br>IR/W<br>IØ2•VMAInte | Erase Enable<br>Fault<br>Fault Reset<br>Head Load<br>Index<br>Interrupt Request<br>Internal Read/Write<br>rnal Phase Two•Valid |

## LEGEND FOR 470 (FLOPPY) BOARD SCHEMATIC

Construction of the Article State

a dia ta

|                      | Address                |

|----------------------|------------------------|

| A4,A5                | Address                |

|                      | Address                |

|                      | ACIA Chip Select       |

|                      | Board Enable           |

|                      | Peripheral A Interrupt |

| UN1, UNE             |                        |

| CD1 CD0 r            | Input-Control Line     |

| UD1,UD2              | Peripheral B Interrupt |

|                      | Input-Control Line     |

| CLR                  | Clear                  |

| DD                   | Data Direction         |

|                      | Data                   |

| DRIVE SELECT         | Drive Select           |

| ERASE ENABLE         | Erase Enable           |

|                      | Fault                  |

|                      | Fault Reset            |

|                      | Head Load              |

|                      | Index                  |

|                      | Interrupt Request      |

|                      | Internal Read/Write    |

|                      | rnal Phase Two-Valid   |

|                      | Memory Address         |

| I OW CURRENT         | Low Current            |

|                      | Port B                 |

|                      |                        |

|                      | Ready Drive One        |

|                      | Ready Drive Two        |

|                      | Read/Write             |

|                      | Sector                 |

|                      | Select Drive One       |

| (Single-Sided Floppy | •                      |

|                      | Select Drive Two       |

| (Single-Sided Floppy | / Interface)           |

| SEPARATED CLOCK      | Separated Clock        |

| SEPARATED DATA       | Separated Data         |

|                      | Side Select            |

| (Dual-Sided Floppy   | Interface)             |

|                      | Step                   |

|                      | Step In                |

|                      | Track Zero             |

|                      |                        |

Any Bar above any alphabetical or numerical combination indicates line active in a low (0) state.

| DD                  | Data Direct                     |

|---------------------|---------------------------------|

| F7XX                | Address F7XX <sub>16</sub>      |

|                     | Address FCXX <sub>16</sub>      |

|                     | Address FDXX <sub>16</sub>      |

| FEXX                | Address FEXX <sub>16</sub>      |

| FFXX <sub>A</sub> . | Address FFXX(6502)              |

| FFXX <sub>B</sub> . | Address FFXX(6800)              |

| HSCK1               | High Speed Clock One            |

| HIS                 | High Speed                      |

| IDO-ID7             | Internal Data                   |

|                     | Internal Data Direct            |

| IIRQ                | Internal Interrupt Request      |

| INMI                | Internal Non-maskable Interrupt |

|                     | Interrupt Request               |

| IR/W                | Internal Read/Write             |

| 1Ø2•VM/             | AInternal Phase Two•Valid       |

|                     | Memory Address                  |

|                     | 10 Memory Address               |

|                     | Memory Request                  |

|                     | Non-maskable Interrupt          |

|                     | Port                            |

|                     | Processor Select High           |

| 20                  | Processor Select Low            |

| PIA RESI            | ETPeripheral Interface          |

|                     | Adapter Reset                   |

|                     | Processor Select                |

|                     | 6502 Select                     |

|                     | 6800 Select                     |

|                     | Z-80 Select                     |

| RAMCE .             | Random Access Memory            |

|                     | Chip Enable                     |

|                     |                                 |

| RDY                 | Ready                           |

|                     | Read Enable(6502)               |

|                     | Read Enable(6800)               |

|                     | Reset                           |

| •                   | Refresh                         |

|                     | Ram Select                      |

| R/W                 | Read/Write                      |

## 505 BOARD (CONTINUED)

| PAO-PA7 PBO-PB7                                                                | Non-Maskable Interrupt<br>Port A<br>Port B<br>Ready Drive One                                                                          |

|--------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------|

| READY DRIVE 2     RES     R/W     SECTOR     SELECT DRIVE 1     SELECT DRIVE 2 | Ready Drive Two<br>Reset<br>Read/Write<br>Sector<br>Select Drive One<br>Select Drive Two<br>Separated Data                             |

| SEP CLOCK                                                                      | Separated Clock<br>Step<br>Step In<br>Track Zero<br>Transmit Clock                                                                     |

| WRITE DATA    WRITE ENABLE    WRITE PROTECT    Ø0    Ø2                        | Valid Memory Address<br>Write Data<br>Write Enable<br>Write Protect<br>Phase Zero<br>Phase Two<br>Phase Two<br>Valid<br>Memory Address |

## LEGEND FOR 510 REV. C BOARD SCHEMATIC

| A0-A19                                    | SS |

|-------------------------------------------|----|

| BØ2Buffer Phase Tw                        | vo |

| BE <sub>A</sub> Bus Enable (Processor 650 | 2) |

| BE <sub>B</sub> Bus Enable (Processor 680 | 0) |

| CLK                                       | ck |

| <code>CS1</code> , 6502 Rom Chip Sele     | ct |

| <b>CS1<sub>8</sub>6800</b> Rom Chip Sele  | ct |

| <b>CS2</b> ,                              |    |

| CS2 <sub>8</sub> 6800 Rom Chip Sele       |    |

| D0-D7Da                                   |    |

|                                           |    |

Any Bar above any alphabetical or numerical combination indicates line active in a low (0) state.

##

## **LEGEND FOR 525 BOARD SCHEMATIC**

| BAO-BA19Backplane Address<br>BDO-BD7Backplane Data<br>BBEBackplane Bus Enable<br>BIEBackplane Input Enable<br>BR/WBackplane Read/Write<br>BØ2 VMABackplane Phase Two-Valid<br>Memory Address |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| CAO-CA19 Port Address                                                                                                                                                                        |

| CBEPort Bus Enable                                                                                                                                                                           |

| CD0-CD7Port Data                                                                                                                                                                             |

| CEO-CE15 Chip Enable For RAM                                                                                                                                                                 |

| CIEPort Input Enable                                                                                                                                                                         |

| CR/WPort Read/Write                                                                                                                                                                          |

| CØ2 VMAPort Phase Two-Valid                                                                                                                                                                  |

| Memory Address                                                                                                                                                                               |

| DD <sub>B</sub> Data Direct Backplane                                                                                                                                                        |

| DD <sub>p</sub> Data Direct Port                                                                                                                                                             |

| MA0-MA13 Memory Address                                                                                                                                                                      |

| MD0-MD7 Memory Data                                                                                                                                                                          |

| MR/WMemory Read/Write                                                                                                                                                                        |

| PC Port Control                                                                                                                                                                              |

| PS Port Status                                                                                                                                                                               |

| WAIT <sub>B</sub> Wait Backplane                                                                                                                                                             |

| WAIT <sub>P</sub> Wait Port                                                                                                                                                                  |

## LEGEND FOR 527 BOARD SCHEMATIC

| A0-A19          |         | . Address |

|-----------------|---------|-----------|

| <b>CEO-CE23</b> | Chip En | able RAM  |

Any Bar above any alphabetical or numerical combination indicates line active in a low (0) state.

## 510 BOARD (CONTINUED)

## LEGEND FOR 520 REV. B BOARD SCHEMATIC

| A0-A17  | Address           |

|---------|-------------------|

| CEO-CE3 | Chip Enable       |

| D0-D7 · | Data              |

| DD      | Data Direction    |

| DIO-DI7 | Data In           |

| D00-D07 | Data Out          |

| R/W     | Read/Write        |

| WAIT    | Wait              |

| Ø2•VMA  | Phase Two • Valid |

|         | Memory Address    |

#### LEGEND FOR 520 REV. C BOARD SCHEMATIC

| A0-A19   | Address          |

|----------|------------------|

| MAO-MA11 | . Memory Address |

| DO-D7    | Data             |

| CEO-CE3  | Chip Enable      |

| DD       | Data Direct      |

| R/W      | Read/Write       |

| MR/WM    | emory Read/Write |

| A8-A19              | Internal Data |

|---------------------|---------------|

| BE                  | Bus Enable    |

| BRGBaud Ra          | ate Generator |

| CS1-CS16            | . Chip Select |

| D0-D7               | Data          |

| DD                  | Data Direct   |

| DE                  | . Data Enable |

| IA0Internal /       | Address Zero  |

| ID0-ID7             | Internal Data |

| IRQ Inter           | rupt Request  |

| IR/W Interna        | al Read/Write |

| IØ2·VMAInternal Pha | se Two•Valid  |

| Mer                 | nory Address  |

| R/W                 | Read/Write    |

| SPR-I               | Spare In      |

| SPR-0               | Spare Out     |

| WAIT                | Wait          |

| Ø2•VMAPha           | se Two•Valid  |

| Mer                 | nory Address  |

## LEGEND FOR 555 BOARD SCHEMATIC

| A0-A15                 | Address                    |

|------------------------|----------------------------|

| ACK                    | Acknowledge                |

| ACSO-ACS3              | ACIA Chip Select           |

| ACS15                  | ACIA Chip Select           |

| BUSY                   | Busy                       |

| CARRIAGE READY .       | Carriage Ready             |

| <b>CARRIAGE STROBE</b> | Carriage Strobe            |

| CE0-CE7                | Chip Enable                |

| СНЕСК                  | Check                      |

| DATA 1-DATA 8          | Data Lines                 |

|                        | (Centronics Interface)     |

| <b>D0-D7</b>           | Data                       |

| DD                     | Data Direct                |

| DL1-DL12D              | ata Line (NEC Interface)   |

| FAULT                  | Fault                      |

| F4XX                   | Address F4XX <sub>16</sub> |

|                        |                            |

## 527 BOARD (CONTINUED)

| <b>DD</b> | Data Direct            |

|-----------|------------------------|

| DO-D7     | Data                   |

| IR/W      | Internal Read/Write    |

| MM        | Memory Management      |

| R/W       | Read/Write             |

| VMA       | . Valid Memory Address |

| WAIT      | Wait                   |

| Y0-Y1-Y2  | Upper Memory Decode    |

| •,        | Phase Zero             |

| Ø2•VMA    | Phase Two • Valid      |

|           | Memory Address         |

## LEGEND FOR 535 BOARD SCHEMATIC

| BE<br>DO-D7<br>DD<br>DIO-DI7<br>DL1-DL16 | Address<br>Bus Enable<br>Data<br>Data Direct<br>Data In<br>Delay<br>Data Out |

|------------------------------------------|------------------------------------------------------------------------------|

| E2                                       | Enable Two                                                                   |

| IØ2                                      | Internal Phase Two                                                           |

| IR/W                                     | Internal Read/Write                                                          |

| MAO-MA6                                  | Memory Address                                                               |

| RASO-RAS2                                | Row Address Strobe                                                           |

| RE                                       | Row Enable                                                                   |

| R/W                                      | Read/Write                                                                   |

| ØOIN                                     | Phase Zero In                                                                |

| ø2                                       | Phase Two                                                                    |

| Ø2•VMA                                   | Phase Two-Valid                                                              |

|                                          | Memory Address                                                               |

| ØDETECT                                  | Phase Detect                                                                 |

## LEGEND FOR 550 BOARD SCHEMATIC

| A0Address Zero |  |

|----------------|--|

| A1-A4 Address  |  |

Any Bar above any alphabetical or numerical combination indicates line active in a low (0) state.

### LEGEND FOR 590 BOARD SCHEMATIC

## 555 BOARD. (CONTINUED)

| F5XX               | Address F5XX <sub>16</sub> |

|--------------------|----------------------------|

|                    | Internal Address           |

|                    | Internal Data              |

|                    | al Interrupt Request       |

|                    | Interrupt Request          |

|                    | Internal Read/Write        |

| IØ2•VMAInter       | nal Phase Two•Valid        |

|                    | Memory Address             |

|                    | Paper                      |

|                    | . Paper Feed Ready         |

|                    | . Paper Feed Strobe        |

|                    | Port 0 Clock               |

|                    | Port 0 In                  |

|                    | Port 0 Out                 |

|                    | Port 1 Clock               |

|                    | Port 1 Out                 |

|                    | Port 2 Clock               |

|                    | Port 2 In                  |

|                    | Port 2 Out                 |

|                    | Port 3 Clock               |

|                    | Port 3 In                  |

|                    | Port 3 Out                 |

|                    | Port 15 Clock              |

| PORT 15 IN         |                            |

|                    | Port 15 Out                |

| PRIME              | Prime                      |

| PRINTER READY      | Printer Ready              |

| P.W. READY         | . Print Wheel Ready        |

| <b>P.W. STROBE</b> | . Print Wheel Strobe       |

| RESTORE            |                            |

|                    | Read/Write                 |

| SELECT             |                            |

| STROBE             |                            |

|                    | Wait                       |

| Ø2•VMA             |                            |

|                    | Memory Address             |

4

| A0 A4F           |                        |

|------------------|------------------------|

|                  | Address                |

|                  | Byte Cycle             |

| <b>BDO-BD7</b>   | Bus Data               |

| BLD              | Byte Load              |

| <b>CBD</b>       | Computer Bus Direction |

|                  | Computer Bus Enable    |

|                  | Character Load         |

|                  | Clear Address          |

|                  | Count                  |

|                  | Disk Control Load      |

|                  | Data Direction         |

|                  |                        |

|                  | Disk Data              |

|                  | Disk Head Address Load |

|                  | Disk Index             |

|                  | Disk Input Status      |

|                  | Disk input Status      |

|                  | ect Memory Access Done |

|                  | Direct Memory Access   |

|                  |                        |

|                  | Done One               |

| DIMA DUNE Z      | Direct Memory Access   |

|                  | Done Two               |

|                  | Direct Memory Access   |

|                  | Register Load          |

| DWA 3K           | Direct Memory Access   |

|                  | Status Register        |

|                  | Disk Read Clock        |

|                  | Disk Read Data         |

|                  | Disk Read Enable       |

|                  | Disk Servo Clock       |

|                  | Disk Write Clock       |

| D WRITE DATA     | Disk Write Data        |

|                  | Disk Write Enable      |

| EL1              | End Load One           |

| EL2              | End Load Two           |

| END <sup>*</sup> |                        |

| G2               | Gate Two               |

|                  |                        |

Any Bar above any alphabetical or numerical combination indicates line active in a low (0) state.

#### LEGEND FOR 592 BOARD SCHEMATIC

A ..... Disk Address A

## 590 BOARD (CONTINUED)

| INDEX          | Index                   |

|----------------|-------------------------|

| IR/W           | Internal Read/Write     |

| I STATUS       | Input Status            |

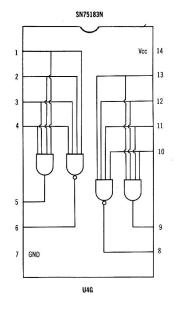

| MDO-MD7        | Memory Data             |

| MAO-MA15       | Memory Address          |

| MDD            | Memory Data Direction   |

|                | Memory Data In          |

| MD00-MD07      | Memory Data Out         |

| MPC            | Memory Process Clear    |

| MPS            | Memory Process Set      |

| MR/W           | Memory Read/Write       |

| MR/W1          | Memory Read/Write One   |

|                | Memory Enable           |

| MØ2•VMA I      | Memory Phase Two-Valid  |

|                | Memory Address          |

| PD             | Partial Decode          |

| <b>RD OFF</b>  | Read Offset             |

| <b>READ CK</b> | Read Clock              |

|                | Read Data               |

|                | . Read Memory Increment |

| RCK            | Read Clock              |

|                | Servo Clock             |

|                | Servo Clock One         |

|                | Seek Strobe             |

|                | Start Load One          |

|                | Start Load Two          |

|                | Start                   |

|                |                         |

|                | Sync                    |

|                | Write Data              |

| WØ2•VMA        | Write Phase Two • Valid |

|                | Memory Address          |

| •.             | Microprocessor Power    |

|                | Phase Two               |

| Ø2•VMA         | Phase Two-Valid         |

|                | Memory Address          |

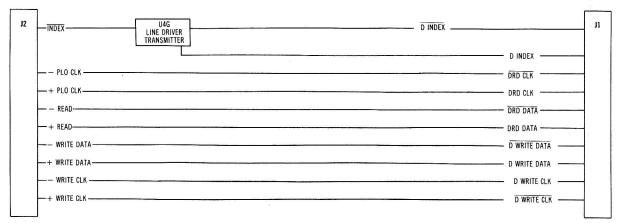

| ADDO-ADD8       | Address Disk             |

|-----------------|--------------------------|

| B               | Disk Address B           |

| <b>C LOAD</b>   | Control Load             |

|                 | Disk Control Load        |

| DDO-DD7         | Disk Data                |

| <b>D HADDL</b>  | Disk Head Address Load   |

| <b>D INDEX</b>  | Disk Index               |

| DI STATUS       | Disk Input Status        |

| DK SEL          | Disk Select              |

| DRD CLK         | Disk Read Clock          |

| <b>DRD DATA</b> | Disk Read Data           |

| D READ EN       | Disk Read Enable         |

| D SCK           | Disk Servo Clock         |

|                 | Disk Write Clock         |

| D WRITE DATA    | Disk Write Data          |

| D WRITE EN      | Disk Write Enable        |

| FHDADDO-FHDADI  | 08 Fixed Head Address    |

|                 | Head Address Load        |

| HDADD1 Head     | d Selection Address Line |

| HDADD2 Head     | d Selection Address Line |

|                 | d Selection Address Line |

|                 | d Selection Address Line |

|                 | Illegal Address          |

|                 | Index A                  |

|                 | Input Status             |

|                 | Maintenance              |

|                 | Moving Head              |

|                 | Current Sense            |

| MHD MULTSEL     | Multiple Moving          |

|                 | Head Selected            |

|                 | Maintenance Mode         |

|                 |                          |

|                 | Offset Forward           |

|                 | Offset Reverse           |

| rwn un          | Power OK                 |

Any Bar above any alphabetical or numerical combination indicates line active in a low (0) state.

•#

| PWR RST Power Reset                 |

|-------------------------------------|

| RDCLKRead Clock                     |

| RDDATARead Data                     |

| READ ENRead Enable                  |

| READY Ready                         |

| RESTORE                             |

| SCK Servo Clock                     |

| SEEK COMPLETE Seek Complete         |

| SEEK LATESeek Late                  |

| SEEK STROBE Seek Strobe             |

| SEEK STROBE DLY Seek Strobe Delayed |

| SEEK STROBE 1Seek Strobe One        |

| STR EARLY Strobe Early              |

| STR LATE Strobe Late                |

| µP POWER Microprocessor Power       |

| WRITE CLK Write Clock               |

| WRITE DATAWrite Data                |

| WRITE EN Write Enable               |

| WRT ADD MK Write Address Mark       |

| 0 HEAD Zero Head                    |

#### **LEGEND FOR 594 BOARD SCHEMATIC**

| C LOAD       | Control Load      |

|--------------|-------------------|

| D INDEX      | Disk Index        |

| DHADDL Disk  | Head Address Load |

| D READ EN    | Disk Read Enable  |

| D WRITE CLK  | Disk Write Clock  |

| D WRITE DATA | Disk Write Data   |

| D WRITE EN   | Disk Write Enable |

| DC LOAD      | Disk Control Load |

### 594 BOARD (CONTINUED)

| <b>DD0-DD7</b>  | Disk Data          |

|-----------------|--------------------|

| DI STATUS       | Disk Input Status  |

| DRD CLK         | Disk Read Clock    |

| DRD DATA        | Disk Read Data     |

| FAULT CLEAR     | Fault Clear        |

| HADDL           | Head Address Load  |

| HD1,HD2,HD4,HD8 | Head Selection     |

|                 | Address Lines      |

| I STATUS        | Input Status       |

|                 | ase Lock Osc Clock |

| <b>READY</b>    | Ready              |

| SEEK COMPLETE   | Seek Complete      |

| STEP DIR        | Step Direction     |

| TRACK 0         | Track Zero         |

| WRITE CLK       | Write Clock        |

| WRITE FAULT     | Write Fault        |

|                 |                    |

#### SCHEMATIC NOTES

--- Circuitry used in some versions.

\* Optional part. Value determined by application = Ground

✓ Common tie point

Chassis

Flame retardant resistor

⊖ See parts list

Item numbers in rectangles appear in the alignment/adjustment instructions.

Supply voltage maintained as shown in input. Voltages measured with digital meter. Terminal indentification may not be found on unit. Resistors are ¼ W or less, 5% unless noted. Value in ( ) used in some versions.

Any Bar above any alphabetical or numerical combination indicates line active in a low (0) state.

## LEGALERY & CLAUSER SINVICES I ENGLISION SOLARY

States States, N. R.

٩

ÿ

1333 S. Chillicothe Road Aurora, Ohio 44202

्व